The RISC-V architecture is relatively new, but the companies that use it to design modern processors (CPU) are increasingly achieving performance which is sometimes comparable to older and popular architectures (ARM, x86, x64, etc.).

Micro Magic, a RISC-V operator, announced recently who designed the world's fastest 64-bit RISC-V processor which beats Apple's M1 chip and ARM Cortex-A9. This CPU is, according to Micro Magic, the embodiment of the vision of David Patterson, vice president of the board of the RISC-V Foundation, for the RISC architecture.

This instruction set architecture is supposed to competes with industry standards such as ARM, whose popularity has exploded in recent years, especially thanks to smartphones.

For example, the ARM-based M1 processor recently introduced by Apple has caused a stir among enthusiasts, analysts, and the IT industry in general. RISC-V is a long way from achieving notoriety for ARM or other instruction set architectures, but the organizations that operate it are claiming record performance.

As such, Micro Magic, a California-based company best known for its Electronic Design Automation (EDA) tools has said that it has been working for a while on what it considers the world's fastest 64-bit RISC-V kernel. To prove it, industry critics have said that the new Micro Magic processor offers decent performance with record-breaking efficiency.

micro-magic claims to be able to load, view and modify the design of more than a trillion transistors in real time. The company was founded in 1995, sold to Juniper Networks for $ 260 million, and in 2004 it was acquired under the same name by the original founders. The founders, Mark Santoro and Lee Tavrow, worked together at Sun Microsystems and led a team that developed a SPARC 300MHz microprocessor.

According to Andy Huang, advisor to Micro Magic and creator of the creation of the FineSim circuit simulator, Santoro also briefed Steve Jobs at Apple.

About a month ago, Micro Magic showed its 64-bit RISC-V kernel to EETimes magazine. The magazine later reported that the core reached 5 GHz and 13.000 CoreMarks at 1,1 V.

The test core was running on an Odroid SBC. This is an important step, but generally a single Micro Magic core operates at 0.8V nominal to provide 11,000 CoreMarks at 4.25GHz, while consuming only 200mW.

Micro Magicc later announced that the same processor could deliver over 8,000 CoreMarks at 3 GHz while consuming only 69 mW of energy.

First of all, what is CoreMark?

It is a deliberately simplified CPU benchmarking tool published by the Embedded Microprocessor Benchmark Consortium (EMBC), designed to be as platform neutral and as simple to build and use as possible.

CoreMark focuses only on the basic functions of the pipeline of a CPU, including basic read / write, integer, and control operations.

This specifically avoids most of the effects of system differences in memory, I / O, etc. EMBC is a widely represented group in the industry: Intel, Texas Instruments, ARM, Realtek and Nokia are some of its most notable and easily recognizable members.

Going back to the M1 chip, Huang tried to explain the importance of Micro Magic's performance compared to Apple's CPU.

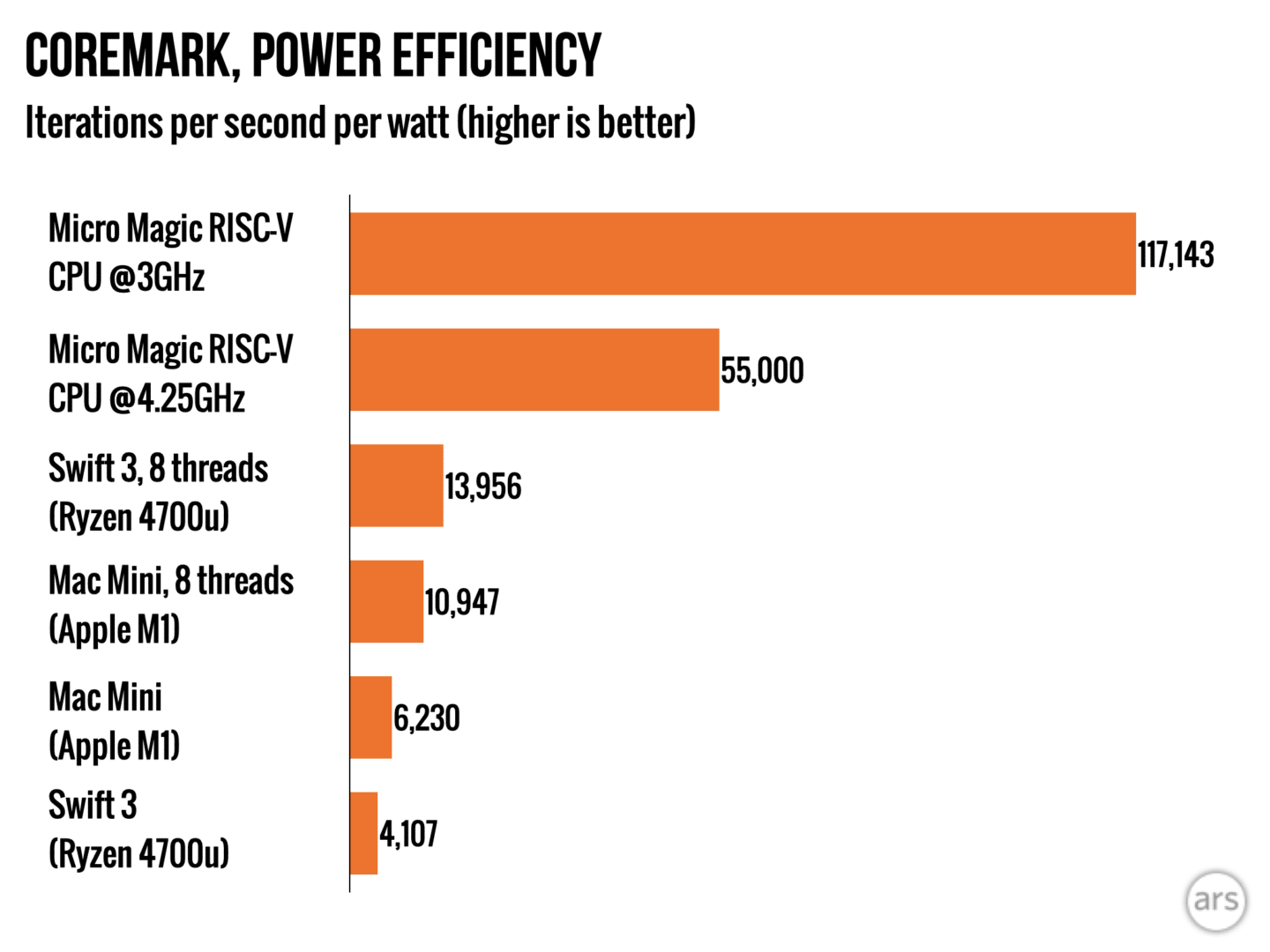

“Using the EMBC benchmark, we get 55.000 CoreMarks per watt. The M1 chip is roughly the equivalent of 10,000 CoreMarks by this same benchmark.

Divide that number by eight cores and 15 W total, and that's less than 100 CoreMarks per watt. The fastest ARM processor by EMBC criteria is the Cortex-A9 (quad-core), with a figure of 22.343 CoreMarks. Divide that number by four cores and 5W per core, and you get 1112 CoreMarks per Watt, ”he said.

He then explained the importance of the 200 mW of power consumption of the new Micro Magic CPU.

“In today's battery-powered devices, CoreMarks per watt are much larger than CoreMarks per Megahertz. For a typical 5W device, we can fit 25 cores. Who can make 25 hearts in the mobile phone industry? Most people are limited to four or eight cores. So for companies that need to reduce battery usage, like Tesla, we can achieve the performance we need, ”he said.

RISC-V looks like it can swallow the world of Hardware, the only thing is the software and adapting everything will be a pain of time and headache I hope that should be the superhero