AMD、Arm、ASE、谷歌云、英特爾公司、Meta、微軟、高通公司、三星和台積電宣布成立一個行業聯盟,將在不同小芯片之間建立標準化互連,並培育一個開放的小芯片生態系統。

通用小芯片互連快遞 (eICU) 是一個標準的開放互連 行業 提供連接性 盒裝高帶寬,低延遲,節能和 在小芯片中獲利。

這是為了滿足預計不斷增長的計算需求, 跨雲、邊緣、企業、5G、汽車、高性能計算和可穿戴設備的連續計算的內存、存儲和連接。 UCIe 旨在提供封裝來自各種來源的芯片的能力,包括不同的製造實驗室、不同的設計和不同的封裝技術。

財團 期待這個標準, 稱為 Universal Chiplet Interconnect Express (UCIe), 允許最終用戶“混合和匹配”組件 用於構建定製片上系統 (SoC) 的多供應商小芯片解決方案。

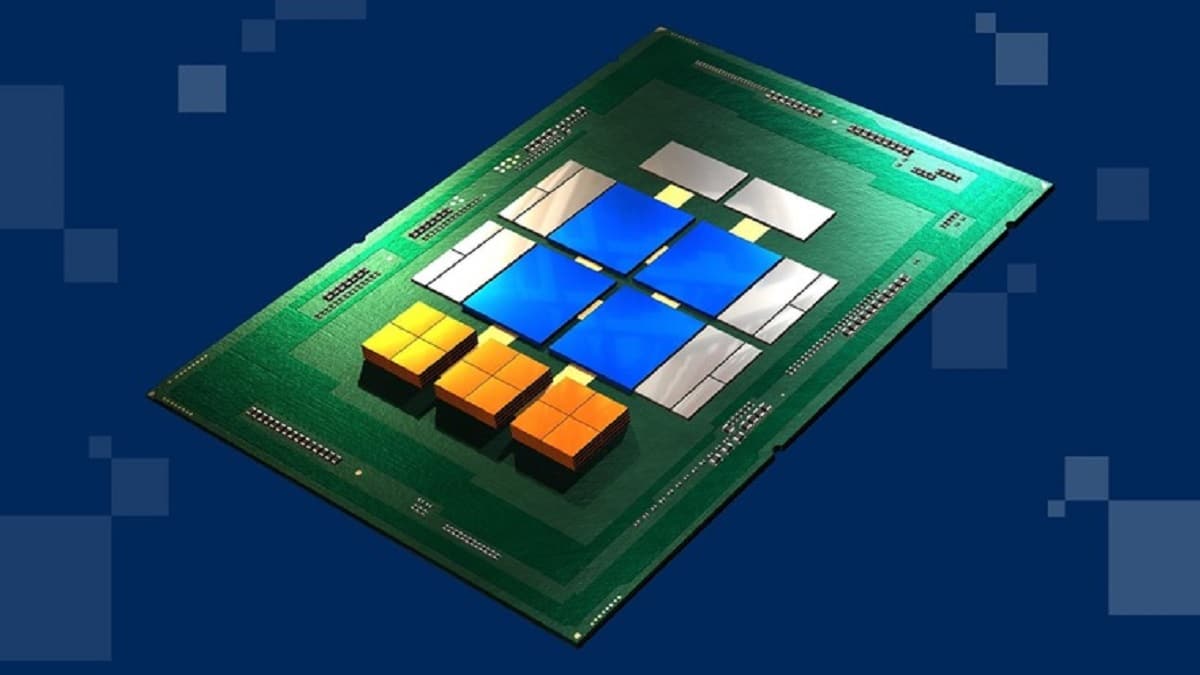

一般來說, 有兩種方法可以構建片上系統 現代(SoC)。 這 單片集成芯片,更傳統的方法, 他們將半導體的所有元素組合成一塊印刷矽片。 反過來, 小芯片採用不同的方法。 不是用所有組件創建一個大芯片,而是小芯片 將事物分解成組件 然後將較小的處理器組合成更大的處理器。

因此,chiplet 的原理是將不同的模塊、chiplet 組合和互連,這些模塊具有自己的矩陣,在單個封裝中。 在某種程度上,這是一個“樂高”模式蒙太奇。

小芯片系統 有一些優點,例如它們可以產生更少的廢物 (例如,如果一個內核發生故障,丟棄兩個 16 核小芯片中的一個要比浪費整個 XNUMX 核單片芯片更容易。) 小芯片設計也具有優勢,因為它允許公司將關鍵組件(例如 CPU 內核)縮小到新的、更小的處理節點,而無需縮小整個 SoC 以進行匹配。 最後,芯片組合允許公司製造比單一單片設計更大的芯片。

最終,為了降低成本和提高性能,現成模塊(小芯片)的市場是完全可能的。 為了使這種做法可行,小芯片之間的互連必須標準化,例如主板使用的不同協議。 這就是 UCIe 想要做的。

英特爾、AMD 和其他公司已經在設計或銷售基於小芯片的處理器 一種或另一種方式:大多數 AMD 的 Ryzen 處理器都使用小芯片,英特爾即將推出的 Sapphire Rapids Xeon 處理器也將使用。

“AMD 很自豪能夠延續其支持行業標準的悠久傳統,這些標準使創新的解決方案能夠滿足客戶不斷變化的需求。 AMD 執行副總裁兼首席技術官 Mark Papermaster 表示,我們一直是小芯片技術的領導者,並歡迎多供應商小芯片生態系統來實現可定制的第三方集成。 “UCIe 標準將通過依賴異構計算引擎和加速器成為刺激系統創新的關鍵因素,從而獲得性能、成本和能源效率方面的最佳優化解決方案。 »

UCIe 項目仍處於早期階段。 目前,標準化過程的重點是建立更大封裝中芯片互連的規則。 但有計劃創建一個 UCIe 行業組織,最終將幫助定義下一代 UCIe 技術,包括未來的“小芯片形式、管理、增強的安全性和其他基本協議”。

這意味著有一天可能會有一個完整的小芯片生態系統,允許公司通過根據他們的需求研究不同的組件來創建定制的 SoC,就像構建遊戲 PC 一樣。

最後,如果你有興趣可以多了解一點,可以查閱詳情 在下面的鏈接中。