AMD, Arm, ASE, Google Cloud, Intel Corporation, Meta, Microsoft, Qualcomm Incorporated, Samsung ו-TSMC הכריזו על הקמת קונסורציום תעשייתי שיקים חיבור סטנדרטי בין שבבים שונים ויטפח מערכת אקולוגית פתוחה של שבבים.

Universal Chiplet Interconnect Express (eICU) הוא חיבור פתוח סטנדרטי של התעשייה שמספק קישוריות בארגז רוחב פס גבוה, זמן אחזור נמוך, חסכוני בצריכת החשמל ו רווחי בין צ'יפלטים.

זה מתוכנן לעמוד בדרישות ההולכות וגדלות הצפוי למחשוב, זיכרון, אחסון וקישוריות על פני מחשוב רציף המתפרש על ענן, קצה, ארגונים, 5G, רכב, מחשוב בעל ביצועים גבוהים וחפצים לבישים. UCIe נועד לספק את היכולת לארוז מתכות ממגוון מקורות, כולל מעבדות ייצור שונות, עיצובים שונים וטכנולוגיות אריזה שונות.

הקונסורציום מצפה לסטנדרט הזה, הנקרא Universal Chiplet Interconnect Express (UCIe), לאפשר למשתמשי קצה "לערבב ולהתאים" רכיבים פתרון שבבים מרובה ספקים לבניית מערכת-על-שבב מותאמת אישית (SoC).

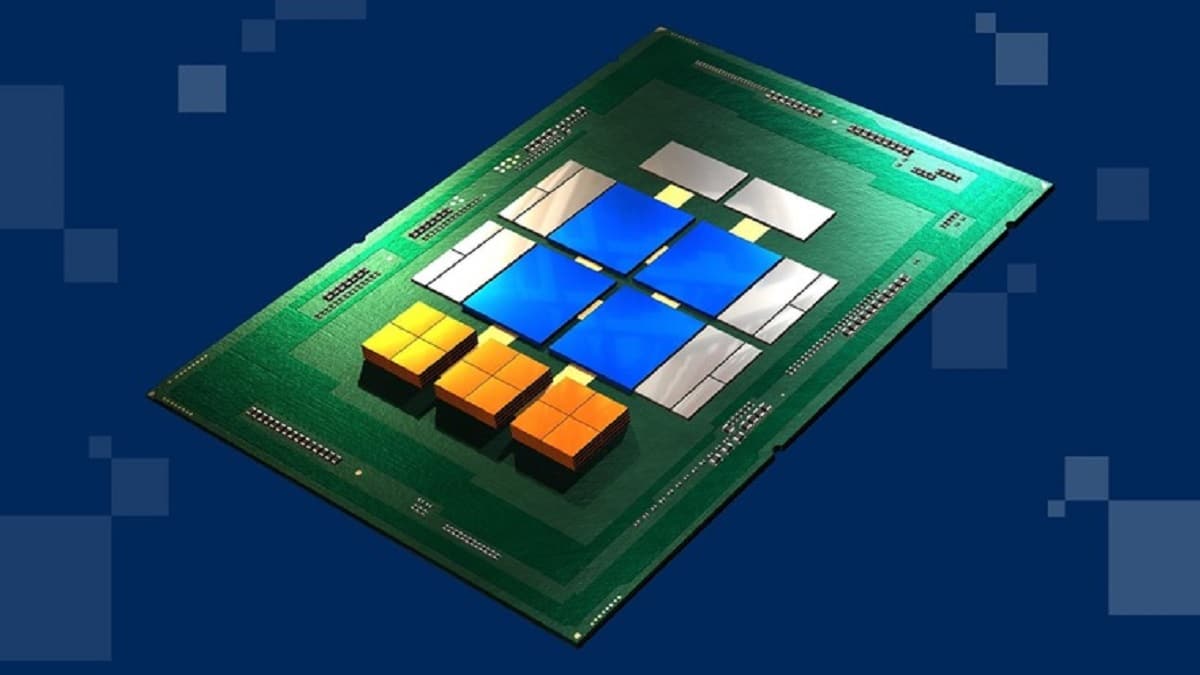

באופן כללי, ישנן שתי דרכים לבנות מערכת על שבב מודרני (SoC). ה שבבים משולבים מונוליטיים, השיטה המסורתית יותר, הם משלבים את כל האלמנטים של מוליך למחצה לתוך חתיכה אחת של סיליקון מודפס. לעומת זאת, צ'יפלטים נוקטים בגישה אחרת. במקום ליצור שבב אחד גדול עם כל הרכיבים, שבבים לפרק דברים לרכיבים קטנים יותר שמשולבים לאחר מכן למעבד גדול יותר.

לכן, העיקרון של chiplets הוא לשלב ולחבר מודולים שונים, chiplets, שיש להם מטריצה משלהם, בתוך חבילה אחת. זה מונטאז' במצב "לגו" במובן מסוים.

מערכת הצ'יפלטים יש כמה יתרונות, שכן למשל הם יכולים לייצר פחות פסולת (לדוגמה, אם ליבה אחת נכשלת, קל יותר לזרוק אחד משני שבבי 16 ליבות מאשר לבזבז שבב מונוליטי שלם בן XNUMX ליבות.) לעיצוב השבבים יש גם יתרונות, שכן הוא מאפשר לחברות לכווץ רכיבים קריטיים (כגון ליבות מעבד) לצמתי עיבוד חדשים וקטנים יותר מבלי לכווץ את כל ה-SoC כדי ליצור התאמה. לבסוף, שילוב שבבים מאפשר לחברות לייצר שבבים גדולים יותר ממה שיכלו עם עיצוב מונוליטי יחיד.

בסופו של דבר, במטרה לצמצם עלויות ולשפר את הביצועים, שוק של מודולים (שבבים) מהמדף הוא אפשרי לחלוטין. רק כדי שתרגול כזה יהיה בר-קיימא, החיבור בין שבבים חייב להיות סטנדרטי, כמו הפרוטוקולים השונים שבהם משתמשים לוח אם, למשל. זה מה שה-UCIe רוצה לעשות.

אינטל, AMD ואחרות כבר מתכננות או מוכרות מעבדים מבוססי שבבים כך או אחרת: רוב מעבדי Ryzen של AMD משתמשים בצ'יפלטים, וגם מעבדי Sapphire Rapids Xeon הקרובים של אינטל יעשו זאת.

"AMD גאה להמשיך את המסורת הארוכה שלה של תמיכה בסטנדרטים בתעשייה המאפשרים פתרונות חדשניים כדי לענות על הצרכים המשתנים של הלקוחות שלנו. היינו מובילים בטכנולוגיית שבבים ומקבלים בברכה מערכת אקולוגית של שבבים מרובת ספקים כדי לאפשר אינטגרציה של צד שלישי להתאמה אישית", אמר Mark Papermaster, סגן נשיא בכיר ומנהל טכני ראשי, AMD. "תקן UCIe יהווה גורם מפתח בגירוי חדשנות במערכת על ידי הסתמכות על מנועי חישוב הטרוגניים ומאיצים שיאפשרו השגת הפתרונות האופטימליים הטובים ביותר מבחינת ביצועים, עלות ויעילות אנרגטית. »

פרויקט UCIe עדיין בשלביו הראשונים. נכון לעכשיו, תהליך הסטנדרטיזציה מתמקד בקביעת כללים לחיבור שבבים בחבילות גדולות יותר. אבל יש תוכניות ליצור ארגון תעשיית UCIe שיעזור בסופו של דבר להגדיר את טכנולוגיית הדור הבא של UCIe, כולל "טפסי שבבים, ניהול, אבטחה משופרת ופרוטוקולים חיוניים אחרים" בעתיד.

המשמעות היא שיום אחד יכולה להיות מערכת אקולוגית שלמה של שבבים שתאפשר לחברות ליצור SoC מותאם אישית על ידי מחקר רכיבים שונים על סמך הצרכים שלהן, בדומה לבניית מחשב גיימינג.

לבסוף, אם אתה מעוניין לדעת קצת יותר על זה, אתה יכול לעיין בפרטים בקישור הבא.