AMD, Arm, ASE, Google Cloud, Intel Corporation, Meta, Microsoft, Qualcomm Incorporated, Samsung en TSMC hebben de vorming aangekondigd van een industrieconsortium dat gestandaardiseerde interconnectie tussen verschillende chiplets tot stand zal brengen en een open chiplet-ecosysteem zal bevorderen.

Universele Chiplet Interconnect Express (eICU) is een standaard open interconnect van de industrie die connectiviteit biedt boxed hoge bandbreedte, lage latentie, energiezuinig en winstgevend onder chiplets.

Dit is gepland om te voldoen aan de verwachte groeiende vraag naar computers, geheugen, opslag en connectiviteit voor continu computergebruik, verspreid over cloud, edge, enterprise, 5G, automotive, high-performance computing en wearables. UCIe is bedoeld om de mogelijkheid te bieden om matrijzen uit verschillende bronnen te verpakken, waaronder verschillende productielaboratoria, verschillende ontwerpen en verschillende verpakkingstechnologieën.

het consortium verwacht deze standaard, genaamd Universal Chiplet Interconnect Express (UCIe), eindgebruikers in staat stellen om componenten te "mixen en matchen" multi-vendor chiplet-oplossing om een custom system-on-chip (SoC) te bouwen.

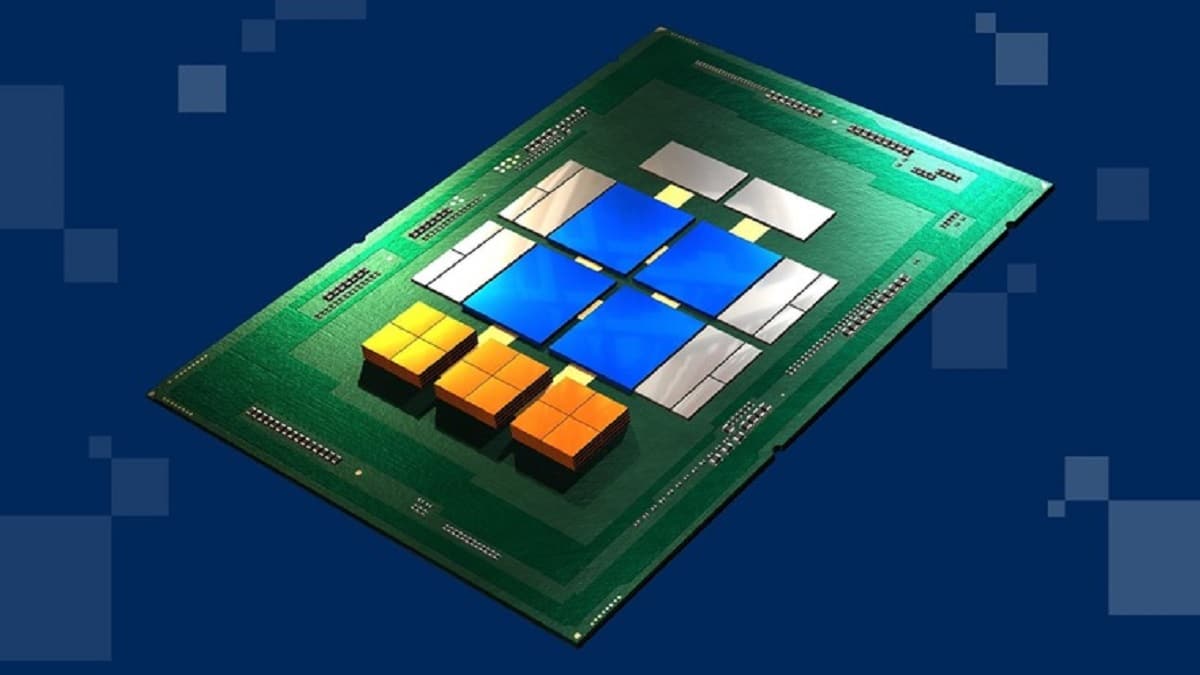

In algemene termen, er zijn twee manieren om een systeem op een chip te bouwen modern (SoC). De monolithische geïntegreerde chips, de meer traditionele methode, ze combineren alle elementen van een halfgeleider in een enkel stuk gedrukt silicium. Omgekeerd, chiplets hebben een andere benadering. In plaats van één grote chip te maken met alle componenten, chiplets dingen opsplitsen in componenten kleinere die vervolgens worden gecombineerd tot een grotere processor.

Daarom is het principe van chiplets om verschillende modules, chiplets, die hun eigen matrix hebben, te combineren en met elkaar te verbinden binnen een enkel pakket. Het is in zekere zin een montage in de "Lego" -modus.

Het chiplet-systeem heeft enkele voordelen, omdat ze bijvoorbeeld minder afval kunnen genereren (Als bijvoorbeeld één core uitvalt, is het makkelijker om een van de twee 16-core chiplets weg te gooien dan een hele XNUMX-core monolithische chip te verspillen.) Het chiplet-ontwerp heeft ook voordelen, omdat het bedrijven in staat stelt kritieke componenten (zoals CPU-cores) te verkleinen naar nieuwe, kleinere verwerkingsknooppunten zonder de hele SoC te hoeven verkleinen om een match te maken. Ten slotte stelt het combineren van chips bedrijven in staat grotere chips te maken dan met een enkel monolithisch ontwerp.

Uiteindelijk is met het oog op kostenreductie en prestatieverbetering een markt voor off-the-shelf modules (chiplets) heel goed mogelijk. Om een dergelijke praktijk levensvatbaar te maken, moet de onderlinge verbinding tussen chiplets worden gestandaardiseerd, zoals de verschillende protocollen die bijvoorbeeld door een moederbord worden gebruikt. Dat is wat de UCIe wil doen.

Intel, AMD en anderen zijn al bezig met het ontwerpen of verkopen van op chips gebaseerde processors Op de een of andere manier: de meeste Ryzen-processors van AMD gebruiken chiplets, en Intel's aankomende Sapphire Rapids Xeon-processors zullen dat ook doen.

“AMD is er trots op zijn lange traditie voort te zetten in het ondersteunen van industriestandaarden die innovatieve oplossingen mogelijk maken om te voldoen aan de veranderende behoeften van onze klanten. We zijn toonaangevend geweest op het gebied van chiplettechnologie en verwelkomen een multivendor chiplet-ecosysteem om aanpasbare integratie van derden mogelijk te maken”, zegt Mark Papermaster, executive vice president en chief technical officer van AMD. “De UCIe-standaard zal een sleutelfactor zijn bij het stimuleren van systeeminnovatie door te vertrouwen op heterogene berekeningsengines en accelerators die het mogelijk zullen maken de best geoptimaliseerde oplossingen te verkrijgen op het gebied van prestaties, kosten en energie-efficiëntie. »

Het UCIe-project bevindt zich nog in de beginfase. Momenteel is het standaardisatieproces gericht op het vaststellen van regels voor het onderling verbinden van chips in grotere pakketten. Maar er zijn plannen om een UCIe-industrieorganisatie op te richten die uiteindelijk zal helpen bij het definiëren van de volgende generatie UCIe-technologie, inclusief "chipletformulieren, beheer, verbeterde beveiliging en andere essentiële protocollen" in de toekomst.

Dit betekent dat er op een dag een heel ecosysteem van chiplets zou kunnen zijn waarmee bedrijven een aangepaste SoC kunnen maken door verschillende componenten te onderzoeken op basis van hun behoeften, net zoals het bouwen van een gaming-pc.

Ten slotte, als u geïnteresseerd bent om er iets meer over te weten, kunt u de details raadplegen In de volgende link.