Arhitektura RISC-V je razmeroma nova, ampak podjetja, ki ga uporabljajo za oblikovanje sodobnih procesorjev (CPU) vedno bolj dosegajo uspešnost kar je včasih primerljivo s starejšimi in priljubljenimi arhitekturami (ARM, x86, x64 itd.).

Napovedal je Micro Magic, operater RISC-V Pred kratkim ki je zasnoval najhitrejši 64-bitni procesor RISC-V ki prekaša Appleov čip M1 in ARM Cortex-A9. Po mnenju Micro Magic je ta procesor utelešenje vizije Davida Pattersona, podpredsednika uprave fundacije RISC-V, za arhitekturo RISC.

Ta arhitektura nabora navodil naj bi tekmuje z industrijskimi standardi, kot so ARM, katerih priljubljenost je v zadnjih letih naglo porasla, predvsem po zaslugi pametnih telefonov.

Na primer, procesor M1 na osnovi ARM, ki ga je pred kratkim predstavil Apple, je povzročil vznemirjenje med navdušenci, analitiki in splošno IT-industrijo. RISC-V je daleč od tega, da bi dosegel prepoznavnost za ARM ali druge arhitekture nabora ukazov, vendar organizacije, ki ga upravljajo, zahtevajo rekordno uspešnost.

Kot tak, Mikro čarovnija, kalifornijsko podjetje, najbolj znano po svojih orodjih za elektronsko oblikovanje (EDA) Povedal je, da že nekaj časa dela na tem, kar se mu zdi najhitrejše 64-bitno jedro RISC-V na svetu. Da bi to dokazali, so industrijski kritiki trdili, da novi procesor Micro Magic ponuja dostojno zmogljivost z rekordno učinkovitostjo.

Mikro čarovnija trdi, da lahko v realnem času naloži, pogleda in spremeni zasnovo več kot bilijona tranzistorjev. Podjetje je bilo ustanovljeno leta 1995, prodano Juniper Networks za 260 milijonov dolarjev, leta 2004 pa so ga z istim imenom kupili prvotni ustanovitelji. Ustanovitelja Mark Santoro in Lee Tavrow sta sodelovala pri podjetju Sun Microsystems in vodila skupino, ki je razvila mikroprocesor SPARC 300 MHz.

Po besedah Andyja Huanga, svetovalca Micro Magic in ustvarjalca ustvarjanja simulatorja vezij FineSim, je Santoro v podjetju Apple seznanil tudi Steva Jobsa.

Pred približno mesecem dni Micro Magic je reviji EETimes pokazal svoje 64-bitno jedro RISC-V. Revija je kasneje poročala, da je jedro doseglo 5 GHz in 13.000 CoreMarkov pri 1,1 V.

Testno jedro je teklo na Odroid SBC. To je pomemben korak, vendar na splošno eno jedro Micro Magic deluje pri nominalni napetosti 0.8 V in zagotavlja 11,000 4.25 CoreMarkov pri 200 GHz, medtem ko porabi le XNUMX mW.

Mikro magijac je kasneje napovedal, da bi lahko isti procesor pri 8,000 GHz dobil več kot 3 CoreMarkov, medtem ko bi porabil le 69 mW energije.

Najprej, kaj je CoreMark?

Gre za namerno poenostavljeno orodje za primerjavo CPU, ki ga je objavil Embedded Microprocessor Benchmark Consortium (EMBC) in je zasnovano tako, da je čim bolj nevtralno za platformo ter čim bolj preprosto za izdelavo in uporabo.

CoreMark se osredotoča le na osnovne funkcije cevovoda CPU, vključno z osnovnimi operacijami branja / pisanja, celo število in nadzor.

S tem se izognemo večini učinkov sistemskih razlik v pomnilniku, vhodno / izhodnih povezavah itd. EMBC je široko zastopana skupina v industriji: Intel, Texas Instruments, ARM, Realtek in Nokia so nekateri izmed njenih najbolj opaznih in lahko prepoznavnih članov.

Če se vrnemo k čipu M1, je Huang poskušal razložiti pomen delovanja Micro Magic v primerjavi z Applovim CPU.

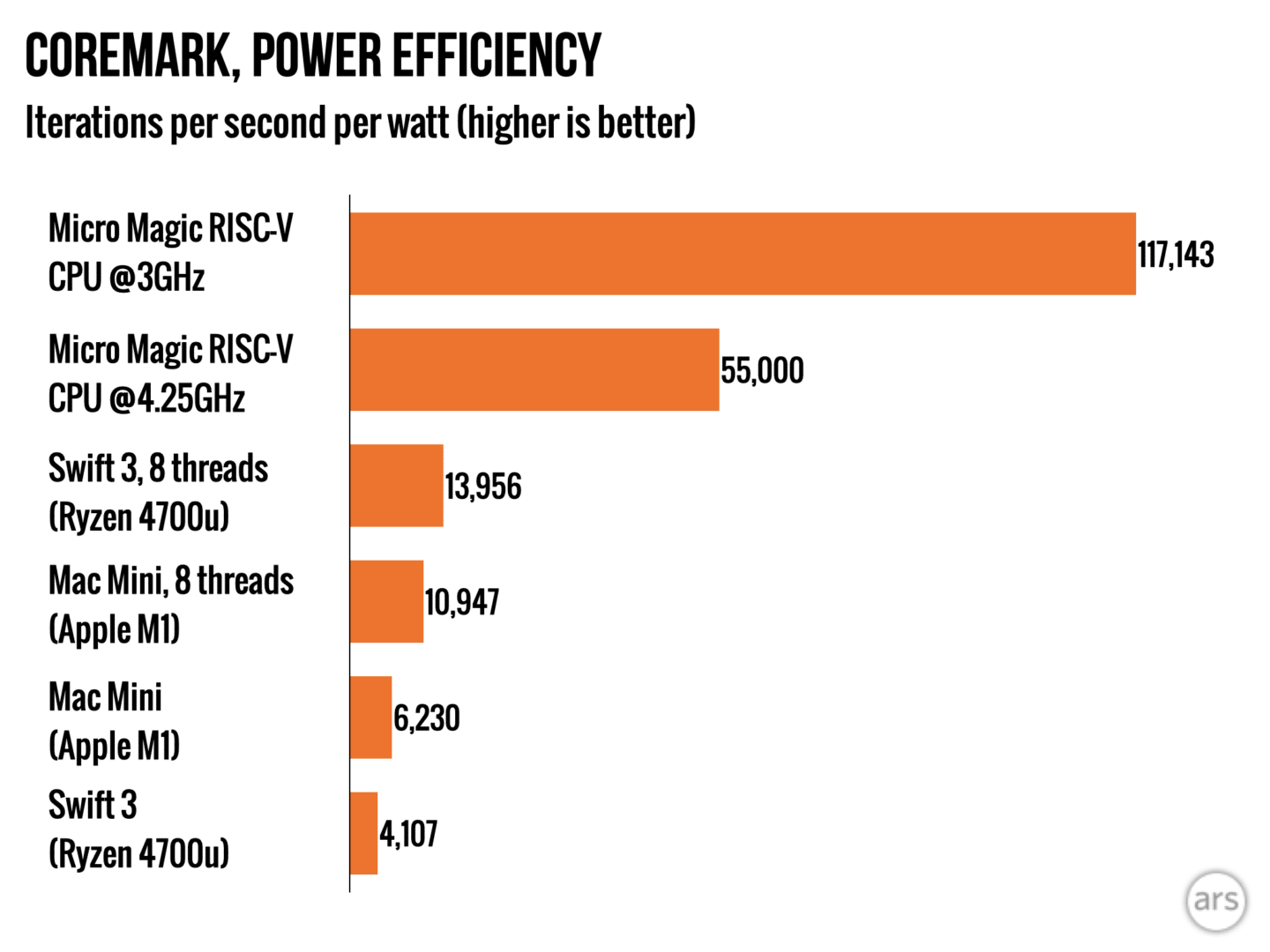

»Z uporabo merila EMBC dobimo 55.000 CoreMarkov na vat. Čip M1 je približno enak 10,000 CoreMarkov po tej isti meri.

To število delite z osmimi jedri in skupno 15 W in to je manj kot 100 CoreMarkov na vat. Najhitrejši procesor ARM po merilih EMBC je Cortex-A9 (štirijedrni) s številko 22.343 CoreMarks. To številko delite s štirimi jedri in 5 W na jedro, in dobite 1112 CoreMarks na Watt, «je dejal.

Nato je pojasnil pomen 200 mW porabe energije novega procesorja Micro Magic.

»V današnjih napravah, ki delujejo na baterije, so CoreMarks na vat veliko večji od CoreMarks na Megahertz. Za tipično 5W napravo lahko namestimo 25 jeder. Kdo lahko izdela 25 src v industriji mobilnih telefonov? Večina ljudi je omejena na štiri ali osem jeder. Tako lahko za podjetja, ki morajo zmanjšati porabo baterije, kot je Tesla, dosežemo potrebno zmogljivost, «je dejal.

Zdi se, da lahko RISC-V pogoltne svet strojne opreme, edina stvar je programska oprema in prilagajanje vsega bo bolečina v času in glavobolu.