AMD, Arm, ASE, Google Cloud, Intel Corporation, Meta, Microsoft, Qualcomm Incorporated, Samsung y TSMC anunciaron la formación de un consorcio industrial que establecerá una interconexión estandarizada entre diferentes chipletsy fomentará un ecosistema abierto de chiplets.

Universal Chiplet Interconnect Express (UCIe) es una interconexión abierta estándar de la industria que proporciona conectividad en caja de alto ancho de banda, baja latencia, eficiencia energética y rentable entre chiplets.

Se planea que esta satisfaga las crecientes demandas proyectadas de cómputo, memoria, almacenamiento y conectividad en todo el cómputo continuo que abarca la nube, el borde, la empresa, 5G, segmentos automotrices, cómputo de alto rendimiento y dispositivos portátiles. Con UCIe se pretende poder brindar la capacidad de empaquetar troqueles de diferentes fuentes, incluidos diferentes laboratorios de fabricación, diferentes diseños y diferentes tecnologías de empaque.

El consorcio espera que este estándar, denominado Universal Chiplet Interconnect Express (UCIe), permita a los usuarios finales «mezclar y combinar» componentes de chiplet de múltiples proveedores para construir un sistema en chip (SoC) personalizado.

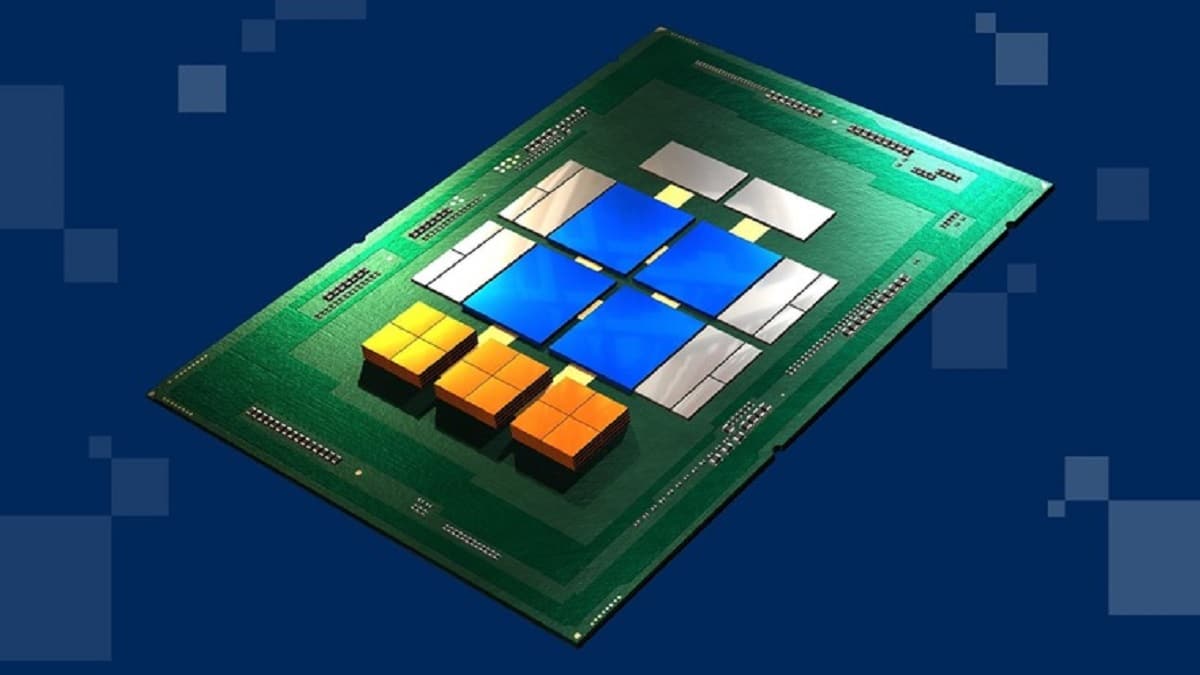

En términos generales, hay dos formas de construir un sistema en chip (SoC) moderno. Los chips integrados monolíticos, el método más tradicional, combinan todos los elementos de un semiconductor en una sola pieza de silicio impreso. Por el contrario, los chiplets adoptan un enfoque diferente. En lugar de crear un gran chip con todos los componentes, los chiplets dividen las cosas en componentes más pequeños que luego se combinan en un procesador más grande.

Por lo tanto, el principio de los chiplets consiste en combinar e interconectar diferentes módulos, chiplets, que tienen su propia matriz, dentro de un mismo paquete. Es un montaje en modo «Lego» en cierto modo.

El sistema de chiplet tiene algunas ventajas, ya que por ejemplo pueden generar menos desperdicio (por ejemplo, si un núcleo falla, es más fácil desechar uno de los dos chiplets de ocho núcleos que desperdiciar un chip monolítico completo de 16 núcleos). El diseño del chiplet también tiene ventajas, ya que permite a las empresas reducir componentes críticos (como núcleos de CPU) a nodos de procesamiento nuevos y más pequeños sin tener que reducir todo el SoC para hacer una combinación. Finalmente, la combinación de chips permite a las empresas fabricar chips más grandes de lo que podrían con un solo diseño monolítico.

En última instancia, con miras a reducir costos y mejorar el rendimiento, es completamente posible un mercado para módulos listos para usar (chiplets). Solo para que tal práctica sea viable, se debe estandarizar la interconexión entre los chiplets, como los diferentes protocolos que utiliza una placa madre por ejemplo. Eso es lo que quiere hacer la UCIe.

Intel, AMD y otros ya están diseñando o vendiendo procesadores basados en chiplet de una forma u otra: la mayoría de los procesadores Ryzen de AMD usan chiplets, y los próximos procesadores Sapphire Rapids Xeon de Intel también lo harán.

“AMD se enorgullece de continuar con su larga tradición de respaldar los estándares de la industria que permiten soluciones innovadoras para satisfacer las necesidades cambiantes de nuestros clientes. Hemos sido líderes en tecnología de chiplet y damos la bienvenida a un ecosistema de chiplet de múltiples proveedores para permitir la integración personalizable de terceros”, dijo Mark Papermaster, vicepresidente ejecutivo y director técnico de AMD. “El estándar UCIe será un factor clave para estimular la innovación de los sistemas al apoyarse en motores de cálculo y aceleradores heterogéneos que permitirán obtener las mejores soluciones optimizadas en términos de rendimiento, coste y eficiencia energética. »

El proyecto UCIe aún se encuentra en sus primeras etapas. Actualmente, el proceso de estandarización se centra en establecer reglas para interconectar chips en paquetes más grandes. Pero hay planes para crear una organización de la industria UCIe que eventualmente ayudará a definir la tecnología UCIe de próxima generación, incluidas «formas de chiplet, administración, seguridad mejorada y otros protocolos esenciales» en el futuro.

Esto significa que algún día podría haber un ecosistema completo de chiplets que permitiría a las empresas crear un SoC personalizado mediante la investigación de diferentes componentes en función de sus necesidades, al igual que construiría una PC para juegos.

Finalmente si estás interesado en poder conocer un poco más al respecto, puedes consultar los detalles en el siguiente enlace.